Sex procents prestandalyft utan att tillverkningen blir dyrare, plus att övriga egenskaper är oförändrade. Intel planerar att som första halvledartillverkare flytta kraftmatningen till undersidan av chipet redan nästa år.

|

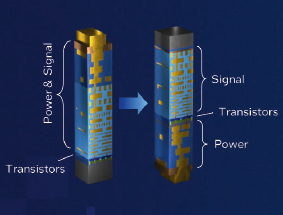

| Genom att flytta kraftmatningen till undersidan blir det mer utrymme för signalledarna vilket förbättrar prestanda och sänker kravet på litografin utan att göra processen dyrare. |

Ledare för signaler och kraftmatning har samsats om utrymmet ovanför transistorerna sedan den integrerade kretsen föddes år 1959. För varje generation har transistorerna blivit mindre men även ledarna har fått hänga med nedåt i skala vilket lett till dagens situation där det är väldigt trångt i de understa ledarlagren.

Det innebär också att inte bara transistorerna i de senaste processerna kräver extremt dyr EUV-litografi, även de understa ledarlagren behöver det. Dessutom ökar spänningsfallet vid drift, så kallad droop, liksom parasiterna. Det senare saktar ned signalerna och därmed även prestanda.

För att mildra problemet har Intel precis som konkurrenterna tittat på möjligheten att sköta kraftmatningen från undersidan. Företaget presenterade resultaten av sina ansträngningar på VLSI Technology and Circuits i Japan i början av juni.

– Vi har en första implementering, vilket är en kritisk milstolpe för oss. Det är en testimplementering som visar fördelarna med Power Via och det prestandalyft kunderna får. Vad vi vet ligger vi före andra i industrin med detta, säger Bernhard Sell på Intel.

PLANEN ÄR ATT BÖRJA använda tekniken redan nästa år i en process på 2 nm kallad 20A som primärt är tänkt för de egna produkterna. Mot slutet av 2024 ska Power Via i 18A-processen bli tillgänglig även för foundry-kunder.

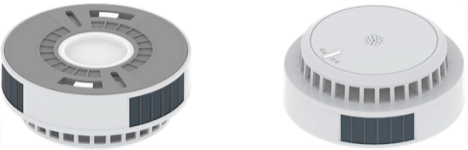

Att flytta kraftmatningen till baksidan av chipen frigör dock inte automatiskt plats för signalledarna om kraftmatningen måste ta omvägen via det understa metallagret, M0. Intels lösning har därför matningen direkt till transistorerna från undersidan med en teknik som företaget döpt till Nano TSV (through silicon via).

|

| Att flytta kraftmatningen till baksidan av chipen frigör inte automatiskt plats för signalledarna om kraftmatningen måste ta omvägen via det understa metallagret, M0, som i mittersta bilden. Intels lösning har därför matningen direkt till transistorerna med en teknik kallad Nano TSV (through silicon via). |

Därmed har det gått att öka avståndet mellan ledarna i lager M0 från 30 nm till 36 nm i testchipet vilket gör processen billigare när kravet på litografin i de understa lagren minskar.

INTEL PLANERAR OCKSÅ att byta transistor i de nya processerna från FinFET till det som företaget kallar Ribbon FET men som annars benämns Gate All Around FET, GAA.

För att inte få samma problem som i den extremt försenade 10 nm-noden, där företaget försökte införa många saker parallellt, har man denna gång valt att testa de två innovationerna separat.

Det som presenteras på VLSI-konferensen i Japan är därför ett testchip med kraftmatningen från baksidan, men med välbeprövade transistorer från dagens 4N-process, det vill säga FinFET.

– Vi har data från tester, vet att det fungerar, att yielden är bra och att värmeproblemen går att hantera och att man har tillgång från baksidan för debugging. Vi har visat att vi kan skapa samma möjligheter som finns idag när man använder Power Via, säger Bern-hard Sell.

Rent praktiskt startar tillverkningen på samma sätt som idag med transistorerna i det understa lagret. Ovanpå det kommer sedan lagren med signalledare.

För att kunna processa undersidan måste ovansidan av wafern bondas fast till en bärare.

Därefter slipas i princip hela undersidan bort tills man nästan är nere vid transistorerna. Sedan tillverkas anslutningarna till transistorerna för kraftmatningen med en via-teknik kallad Nano CPV. Slutligen tillverkas ett antal lager för ledarna till kraftmatningen.

NU ÄR DET DAGS att slipa bort större delen av bäraren för att värmen som utvecklas vid användning ska kunna ledas bort.

Jämfört med dagens process tillkommer alltså steg i tillverkningen för att bonda fast wafern på en bärare och sedan slipa bort först baksidan och sedan framsidan vilket kräver nya maskiner.

– Även om det adderar processteg kan vi förenkla metallagren, så tittar man på processflödet ökar det inte tiden mycket.

Det påverkar inte heller kapslingen eller möjligheten att använda chipen som chiplets i avancerade byggsätt.

– En fundering när man slipar ned baksidan är om transistorerna uppför sig som i Intel 4 eller om det blir andra tillförlitlighetsproblem.

Av de två papper som företaget presenterade på konferensen i Japan framgår att testchipen klarade sig galant. Yielden är i princip oförändrad och det har inte dykt upp några problem med värmeavledning. Dess-sutom går det att precis som tidigare skapa teststrukturer på baksidan vilket behövs för avlusning. Inte heller utnyttjandegraden av logikcellerna försämrades.

Testchipet bestod av fyra processorkärnor i Meteor Lakefamiljen, närmare bestämt Crestmont.

OM INGET OVÄNTAT tillstöter kommer Power Via i produktion redan nästa år.

– Vi är tillbaka i ledartröjan precis som vi var med strained silicon, high K metal gates och FinFET:s. Vi var först och marknaden följde efter, säger Bernhard Sell.

Artikeln är tidigare publicerad i magasinet Elektroniktidningen. Artikeln är tidigare publicerad i magasinet Elektroniktidningen.Prenumerera kostnadsfritt! |

Och tittar man i kristallkulan kan det dyka upp fler saker på baksidan. Två heta kandidater är RAM-minne och flash-minne.